# ACS APPLIED MATERIALS & INTERFACES

# Electrical Contact at the Interface between Silicon and Transfer-Printed Gold Films by Eutectic Joining

Hohyun Keum,<sup>†</sup> Hyun-Joong Chung,<sup>‡</sup> and Seok Kim\*<sup>,†</sup>

<sup>†</sup>Department of Mechanical Science and Engineering, University of Illinois at Urbana–Champaign, Urbana, Illinois 61801, United States

<sup>‡</sup>Department of Chemical and Materials Engineering, University of Alberta, Edmonton, Alberta T6G 2V4, Canada

**Supporting Information**

**ABSTRACT:** This paper presents the electrical and morphological properties at the interface between a metal (Au) and a semiconductor (Si) formed by a novel transfer-printing technology. This work shows that a transfer-printed thin (hundreds of nanometers) Au film forms excellent electrical contact on a Si substrate when appropriate thermal treatment is applied. The successful electrical contact is attributed to eutectic joining, which allows for the right amount of atomic level mass transport between Au and Si. The outcomes suggest that transfer-printing-based micromanufacturing can realize not only strong mechanical bonding but also high-quality electrical contact via eutectic joining.

KEYWORDS: transfer printing, contact resistance, transmission line model, eutectic bonding, metal-semiconductor contact

## INTRODUCTION

Transfer printing involves the use of a soft stamp to transfer solid micro/nanoscale materials from a substrate where they are generated or grown to a different substrate for device integration. $^{1-4}$  This technique has been emerging because of its attractive capabilities of heterogeneous material integration<sup>5-9</sup> and assembly of common electronic devices on soft substrates to fabricate flexible electronics.<sup>10-15</sup> Besides, transfer printing has been explored to manufacture microsystems particularly when combined with direct-bonding techniques such as silicon fusion bonding via annealing.<sup>16</sup> The transferprinting-based micromanufacturing (termed "micromasonry")<sup>16</sup> enables the three-dimensional adhesiveless deterministic assembly of homogeneous as well as heterogeneous materials at microscale. Because of the adhesiveless assembly capabilities, it has the potential to impact numerous vital microsystems that cannot easily be accommodated with other existing methods.<sup>16–18</sup> In spite of its capability to create enormous applications, many scientific and technological aspects of transfer-printing-based micromanufacturing have not yet been explored. For example, the thermal conductance at the interface between a transfer-printed gold (Au) film and a smooth silicon (Si) substrate was recently investigated and turned out to be only a factor of 3 smaller than that of the corresponding interface formed by vacuum deposition.<sup>19</sup> Other interfacial properties that are important but have not yet been explored include optical and electrical contacts.

Here, we present an electrical contact resistance of the interface between gold (Au) thin films and silicon (Si) assembled via transfer printing. We transfer-printed Au films onto a Si substrate to make a sample and annealed the sample

at different temperatures for different time durations to modulate the contact resistance between Au and Si. A transmission line model (TLM) was employed to measure the contact resistance of the samples. The collected data were compared with the contact resistance for a counterpart interface between sputtered Au with a chromium (Cr) adhesive layer and Si, which is commonly used in microfabrication. Our experimental results reveal that the contact resistance of transfer-printed Au films and Si is comparable to the contact resistance of its vacuum-deposited counterpart when appropriate thermal treatment is followed. Specifically, annealing at a temperature slightly above the bulk eutectic ( $\sim$ 360 °C) for less than 30 min provides excellent electrical contact with smooth Au film morphology. Annealing for a longer time and/or at higher temperature causes a rupture in the Au film. Annealing at a temperature below the bulk eutectic results in a high electrical contact resistance. A comparison with the literature suggests that the quality of the electrical contact via transfer printing and subsequent annealing is nearly the same as the known values for the interface of vacuum-deposited Au and Si substrates (see the Supporting Information). This outcome proves that transfer-printing-based micromanufacturing, i.e., micromasonry, can develop the interface between assembled heterogeneous materials with significantly low electrical contact resistance.

Received: March 5, 2013 Accepted: June 10, 2013 Published: June 10, 2013

## RESULTS AND DISCUSSION

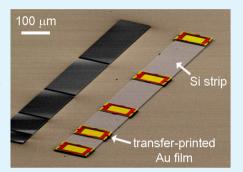

Figure 1 demonstrates the schematic illustration of the transferprinting procedure of 400 nm thick, 100  $\mu$ m × 100  $\mu$ m Au films

**Figure 1.** Schematic view of the fabrication procedure: (a) donor substrate with 400-nm-thick,  $100 \ \mu m \times 100 \ \mu m$  Au films; (b) retrieval of the film using an elastomeric stamp; (c) printing of the retrieved film on a Si strip with spacings of 200, 300, and 400  $\mu m$ ; (d) SEM image of a fully fabricated Si strip with Au films and a neighboring patterned Si that was used as an alignment mark during transfer printing.

that are prepared on a donor substrate through the fabrication process developed elsewhere<sup>19</sup> (see the Supporting Information) and a scanning electron microscopy (SEM) image of Au films on a Si strip assembled via micromasonry. First, Au films with photoresist frames are retrieved from a donor substrate and printed on a highly doped ( $\rho = 0.001 - 0.006 \ \Omega \cdot cm$ ) Si strip, which was patterned on the top of a SiO<sub>2</sub> layer of a receiver substrate. Adjacent to this Si strip are a set of patterned Si islands that were used as alignment marks during transfer printing. Next, the substrate with printed Au films and the Si strip were placed into a rapid thermal-annealing furnace and annealed at various temperatures for various durations to enhance the strength of the adhesion between the Au films and the Si strip. This annealing step completed the preparation of the sample of Au-Si for the following TLM measurement. In order to validate the electrical contact resistance for the prepared sample, a control sample was also prepared through conventional microfabrication. 400-nm-thick Au films with 2nm-thick Cr adhesive layers were patterned on a Si strip through sputter deposition in the control sample.

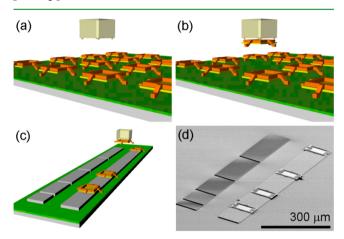

A total of 12 samples with different annealing conditions in terms of temperature and duration are summarized in Figure 2a. For these samples, the surface morphology of the Au films and the electrical contact resistance of transfer-printed Au films and Si strips were characterized. Four distinctive categories were identified, which we denote as regimes A-D. The surface morphology of the samples was examined through SEM images. Figure 2b represents the surface morphology seen from Au films annealed with the conditions of regimes A and B. Here, the root-mean-square (RMS) roughness of the Au films was less than 10 nm, measured by atomic force microscopy (AFM) at a scan size of 20  $\times$  20  $\mu$ m<sup>2</sup>. While the Au films in regimes A and B are not as smooth as the vacuum-deposited Au-Cr surface (RMS of 0.85 nm), they showed identically smooth and flat morphology without any significant alteration. As shown in Figure 2c, the surface became considerably

**Research Article**

**Figure 2.** (a) Different regimes with different annealing conditions based on the morphology change and the electrical contact resistance of transfer-printed Au films, (b) the unaltered surface morphology for regimes A and B, (c) the roughened surface morphology for regime C, and (d) the ruptured surface morphology for regime D. All scale bars represent 50  $\mu$ m.

roughened in regime C with RMS roughness of 50-70 nm. In spite of the surface roughness, the Au films in regime C completely covered the Si strip; thus, their functionality as metal contact pads on the semiconductor was still valid. However, Au films annealed at 400 °C in regime D exhibited undesirable ruptured surfaces (Figure 2d). In this regime, the bare Si surface is exposed; thus, the Au films cannot function as metal contact pads.

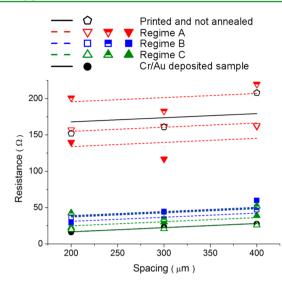

While the surface morphology indicates the structural validity of Au films as a metal pad on silicon, the quality of the electrical contact between the two different materials can be quantified by contact resistance. Contact resistances were collected by plotting current-voltage (I-V) curves using a probe station (4155c semiconductor parameter analyzer, Agilent). Between two adjacent Au films, a voltage bias from -0.1 to +0.1 V was applied and the current were simultaneously measured. From the obtained current and voltage values, the total resistance  $(R_{\rm T})$  between two Au films with various spacing was plotted in Figure 3. The total resistance consists of 2 times the interfacial contact resistance between the Au film and highly doped Si strip  $(R_C)$  and the access resistance, which is the sheet resistance of Si  $(R_{SH})$  times the spacing between two probed Au films (d) divided by the width of the Au films (w). Assuming that  $R_{\rm C}$  does not change when d is varied, the equation for  $R_{\rm T}$ is<sup>20-22</sup>

$$R_{\rm T} = 2R_{\rm C} + \frac{R_{\rm SH}d}{w} \tag{1}$$

From eq 1, the *y* intercept is 2 times the contact resistance between Si and Au and the slope represents the sheet resistance of the Si strip. Contact resistance ( $R_C$ ) data obtained from linear regressions in Figure 3, where a fixed slope value from the sputter-deposited film is used, are summarized in Table 1. As can be seen from the table, regime A, where the samples are annealed below 360 °C or nonannealed, exhibits a much larger contact resistance than other samples annealed at or above 360 °C. A detailed description of the electrical properties in regime A is described in the Supporting Information. The contact resistance values for the samples annealed in regimes B and C

**Figure 3.** Plot of the total resistance versus spacing between two adjacent Au films. Different marks represent different annealing conditions, as described in Figure 2.

Table 1. Contact Resistance  $(R_{C}, \Omega)$  Values from Figure 3<sup>*a*</sup>

|                  | duration            |                     |                     |

|------------------|---------------------|---------------------|---------------------|

| temperature (°C) | 5 min               | 30 min              | 60 min              |

| 380              | 27.60               | 5.14                | 25.67               |

| 360              | 26.50               | 19.68               | 13.48               |

| 350              | 184.23 <sup>b</sup> | 126.23 <sup>b</sup> | 143.57 <sup>b</sup> |

sputtered Au/Cr 5.37

<sup>*a*</sup>A fixed slope value (0.057  $\Omega/\mu$ m) was used for linear fitting. <sup>*b*</sup>R<sub>C</sub> after the "burn-in" process (see the Supporting Information).

were remarkably small. They are only a factor of 1-5 larger than the contact resistance for Au films with Cr adhesive layers sputter-deposited on Si. The contact resistance of the samples in regime D was not measurable because Au films were ruptured during annealing.

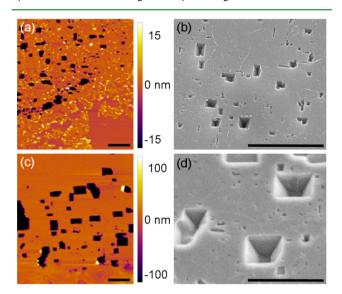

A useful metal contact on a semiconductor requires a minimal loss of the electrical current at the interface between a metal and a semiconductor. In addition, it is preferred that the metal contact do not roughen to rupture or develop hillocks during the fabrication process. From a quick glance of Figure 3, one can postulate that an annealing temperature of 360 °C makes a sharp transition that divides "poor" (regime A) and "good" (regimes B and C) electrical contacts. However, a longer annealing time for temperatures at or above 360 °C can cause a roughening in the surface morphology, leading to a ruptured Au film in regime D. This rupture becomes instantaneous at or above 400 °C of annealing. In this study, regime B showed an optimized process window with reasonable electrical contact resistance and smooth Au film morphology. In order to understand the underlying mechanism that drives the electrical joining of the transfer-printed Au on Si, it is useful to revisit fundamental concepts from studies on the interface between vacuum-deposited Au and Si. Pure Si and Au exhibit high melting temperatures of ~1060 and ~1410 °C, respectively. However, alloying at the interface significantly decreases the melting temperature to as low as  $\sim$ 360 °C at a composition ratio of 19 atom % of Si.<sup>23</sup> This is called eutectic melting. In addition to eutectic melting, interfacial mixing between Au and Si is known to take place at significantly lower temperature than the eutectic melting point, even at room temperature.<sup>24–29</sup> In our study, we observed Si diffusion into the Au film at all annealing temperatures (350-400 °C). Interface morphology after annealing can be directly visualized by AFM and SEM in Figure 4 by etching Au with an iodine-

**Figure 4.** AFM and SEM images of Si strips after etching Au films: (a and b) annealing conditions of 350 °C for 30 min; (c and d) annealing conditions of 360 °C for 60 min. All scale bars represent 2  $\mu$ m.

based wet etchant. Pits are the sites that Si atoms diffused out of the wafer. The reverse pyramidal shape in the (100) wafer stems from the anisotropic nature of Au–Si interaction, where the  $\langle 111 \rangle$  plane has the highest atomic density, thus the slowest in losing the atoms.<sup>30</sup> It is notable that regimes A and B, where the electrical contact is poor and good, respectively, have qualitatively identical internal morphologies in parts b and d of Figure 4, respectively. The larger pits in Figure 4d can readily be understood as a kinetic effect that more Si atoms diffuse out at higher temperature (360 vs 350 °C) for longer time (60 vs 30 min).

A rather striking feature is the sharp transition of the electrical contact at 360 °C for regimes A vs B and C. For example, annealing for 2 h at 350 °C leads to poor contact, whereas 5 min at 360 °C is sufficient to make a good contact (see the Supporting Information). However, the internal morphology in Figure 4 clearly suggests the intermixing of Au and Si at the interface for both temperatures. In fact, the poor electrical contact in spite of the interfacial Au-Si mixing was previously reported for 200 °C annealed Au coatings on the (100) Si wafer.<sup>31</sup> In order to reconcile the discrepancy between the electrical and morphological properties, we suggest two possible explanations. The first possibility is the formation of electrically insulating silicide, which tends to dissociate at annealing temperatures of 360 °C and above. At thermodynamic equilibrium, the Au-Si system does not possess stable silicides. However, it was previously reported that crystalline silicides form at lower temperatures, whereas they dissociate into pure Au and Si phases at ~400 °C.<sup>32,33</sup> To our knowledge, the electrical properties of the low-temperature silicides have not been reported. The second possibility is microvoid formation and their relaxation by the reflow of Au-Si eutectic melts. When atoms in crystalline Si diffuse into a thick film of

## **ACS Applied Materials & Interfaces**

Au, it is known that voids form because of the volume mismatch between the two phases.<sup>34</sup> We postulate that the voids can heal above the bulk eutectic temperature ( $\sim$ 360 °C), where the collective motion of Au atoms can possibly backflow into the voids. This is in logical agreement with the fact that eutectic bonding requires an annealing temperature above eutectic and is often accompanied with pressure<sup>23,35–38</sup> even if Au–Si intermixing takes place at much lower temperatures. These explanations are somewhat speculative, but we hope that these arguments will stimulate future studies on the interface between Si and a thick Au film with an emphasis on the electrical properties.

Finally, the morphological evolution from regimes B to C to D with increasing temperature and annealing duration can be explained as Au dewetting from the Si surface accelerated by interdiffusion of Au and Si. It has been well-known that Au films on the Si surface are thermodynamically unstable and thus bead up to form individual islands.<sup>39</sup> For our transfer-printed Au films, however, a kinetic pathway must be provided to cause the Au film to rupture. Otherwise, the film morphology may stay smooth for prolonged periods of time even though the smooth pad is not thermodynamically stable. In the case of our Au films in regimes B–D, however, the interdiffusion of Au and Si at the interface causes local stress due to density mismatch, followed by mass flow of the Au-Si eutectic melt for stress relaxation. The interdiffusion and mass flow serve as a pumping mechanism for materials, which leads to roughened films in regime C and ultimately ruptured films in regime D. In summary, regime D is an ultimate stable morphology, whereas regimes B and C are quenched morphologies pinned by cooling to room temperature. Therefore, in order to fabricate a useful Au contact pad on Si by transfer printing, one must set the annealing temperature right above the eutectic melting and keep the annealing time short, followed by quenching to room temperature.

## CONCLUSION

The electrical contact properties of transfer-printed Au films on Si substrates were explored as a function of the subsequent annealing conditions. Au-Si contact resistance values for the samples prepared with 12 different combinations of the annealing temperature and duration were measured using TLM, and their surface morphology alteration was examined. A transfer-printed Au film on Si exhibits significantly reduced contact resistance, comparable to that of vacuum-deposited Au on Si, when annealed at or above the bulk eutectic temperature. The surface of Au, however, roughens during the annealing process; thus, a controlled thermal treatment is required to fabricate useful metal-semiconductor contact using transfer printing. The drastic change of the contact resistance and surface morphology is attributed to the atomic-level mass transport between transfer-printed Au and Si, leading to their eutectic joining and Au dewetting. The findings in this work suggest that high-quality metal contact on the semiconductor can be realized via transfer-printing-based micromanufacturing, which complements conventional microfabrication.

## ASSOCIATED CONTENT

## **Supporting Information**

Experimental procedure, current–voltage (I-V) characteristics for poor electrical contact, and contact resistance between vacuum-deposited Au and Si. This material is available free of charge via the Internet at http://pubs.acs.org.

## AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: skm@illinois.edu.

## Author Contributions

The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript. H.K. and H.-J.C. contributed equally to this work.

## Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors thank K.-I. Jang, Y. M. Song, and S. I. Rhee for their help with processing and discussion, S. Maclaren and H. Kim for his assistance in AFM imaging, and J. Rogers for thoughtful discussion.

## REFERENCES

(1) Meitl, M.A.; Zhu, Z.-T.; Kumar, V.; Lee, K. J.; Femg, X.; Huang, Y. Y.; Adesida, I.; Nuzzo, R. G.; Rogers, J. A. *Nat. Mater.* **2006**, *5*, 33–38.

(2) Kim, S.; Carlson, A.; Cheng, H.; Lee, S.; Park, J.-K.; Huang, Y.; Rogers, J. A. Appl. Phys. Lett. 2012, 100, 171909–171909-4.

(3) Panzer, M. J.; Aidala, K. E.; Bulović, V. Nano Rev. 2012, 3, 16144-16144-8.

(4) Hines, D. R.; Mezhenny, S.; Breban, M.; Williams, E. D.; Ballaroto, V. W.; Esen, G.; Southard, A.; Fuhrer, M. S. *Appl. Phys. Lett.* **2005**, *86*, 163101–163101-3.

(5) Kim, S.; Su, W.; Mihi, A.; Lee, S.; Liu, Z.; Bhandakkar, T. K.; Wu, J.; Geddes, J. B., III; Johnson, H. T.; Zhang, Y.; Park, J.-K.; Braun, P. V.; Huang, Y.; Rogers, J. A. *Small* **2012**, *8*, 901–906.

(6) Watson, M. W. L.; Abdelgawad, M.; Ye, G.; Yonson, N.; Trottier, J.; Wheeler, A. R. Anal. Chem. 2006, 78, 7877–7885.

(7) Kang, S. J.; Kim, B.; Kim, K. S.; Zhao, Y.; Chen, Z.; Lee, G. H.; Hone, J.; Kim, P.; Nuckolls, C. *Adv. Mater.* **2011**, *23*, 3531–3535.

(8) Chung, H.-J.; Kim, T.-I.; Kim, H.-S.; Wells, S.-A.; Jo, S.; Ahmed, N.; Jung, Y. H.; Won, S. M.; Bower, C. A.; Rogers, J. A. Adv. Funct. Mater. **2011**, *21*, 3029–3036.

(9) Wang, L.; Yoon, M.-H.; Lu, G.; Yang, Y.; Facchetti, A.; Marks, T. J. Nat. Mater. **2006**, *5*, 893–900.

(10) McAlpine, M. C.; Ahmad, H.; Wang, D.; Heath, J. R. Nat. Mater. **2007**, *6*, 379–384.

(11) Barr, M. C.; Rowehl, J. A.; Lunt, R. R.; Xu, J.; Wang, A.; Boyce, C. M.; Im, S. G.; Bulović, V.; Gleason, K. K. *Adv. Mater.* **2011**, *23*, 3500–3505.

(12) Moonen, P. F.; Yakimets, I.; Huskens, J. Adv. Mater. 2012, 24, 5526–5541.

(13) Jeon, J.; Lee, H.-B.; Bao, Z. Adv. Mater. 2013, 25, 850-855.

(14) Hines, D. R.; Ballarotto, V. W.; Williams, E. D.; Shao, Y.; Solin,

S. A. J. Appl. Phys. 2007, 101, 024503-024503-3.

(15) Hines, D. R.; Southard, A.; Fuhrer, M. S. J. Appl. Phys 2008, 104, 024510–024510-3.

(16) Keum, H.; Carlson, A.; Ning, H.; Mihi, A.; Eisenhaure, J. D.; Braun, P. V.; Rogers, J. A.; Kim, S. J. Micromech. Microeng. **2012**, 22, 055018–055018-7.

(17) Keum, H.; Seong, M.; Sinha, S.; Kim, S. Appl. Phys. Lett. 2012, 100, 211904–211904-4.

(18) Zhang, Y.; Keum, H.; Kim, S. Microassembly of MEMS actuators and sensors via micro-masonry. IEEE International Conference for MEMS, Taipei, Taiwan, Jan 2013.

(19) Oh, D.-W.; Kim, S.; Rogers, J. A.; Cahill, D. G.; Sinha, S. Adv. Mater. **2011**, 23, 5028–5033.

(20) Reeves, G. K.; Harrison, H. B. *IEEE Electon Device Lett.* **1982**, *3*, 111–113.

(21) Schroder, D. K. Semiconductor material and device characterization, 3rd ed.; John Wiley & Sons, Inc.: Hoboken, NJ, 2006.

## **ACS Applied Materials & Interfaces**

(22) Stavitski, N.; van Dal, M. J. H.; Wolters, R. A. M.; Kovalgin, A. Y.; Schmitz, J. Specific contact resistance measurements of metal semiconductor junctions. IEEE International Conference for ICMTS, Austin, TX, Mar 2006.

(23) Wolffenbuttel, R. F.; Wise, K. D. Sens. Actuators, A 1994, 43, 223-229.

(24) Hiraki, A. Surf. Sci. Rep. 1984, 3, 357-412.

(25) Zhang, M.; Wen, J. G.; Efremov, M. Y.; Olson, E. A.; Zhang, Z. S.; Hu, L.; de la Rama, L. P.; Kummamuru, R.; Kavanagh, K. L.; Ma, Z.; Allen, L. H. J. Appl. Phys. **2012**, 111, 093516–093516-7.

(26) Molodtsov, S. L.; Laubschat, C.; Kaindl, G.; Shikin, A. M.;

Adamchuk, V. K. *Phys. Rev. B* **1991**, *44*, 8850–8857.

(27) Calandra, C.; Bisi, O.; Ottaviani, G. Surf. Sci. Rep. 1985, 4, 271–271-3.

(28) Hoshino, Y.; Kitsudo, Y.; Iwami, M.; Kido, Y. Surf. Sci. 2008, 609, 2089–2095.

(29) Kim, J. H.; Yang, G.; Yang, S.; Weiss, A. H. Surf. Sci. 2001, 475, 37–46.

(30) Chen, P. H.; Lin, L.; Liu, C. Y. Appl. Phys. Lett. 2007, 90, 132120-132120-3.

(31) Young, T. F.; Chang, J. F.; Ueng, H. Y. Thin Solid Films 1998, 322, 319-322.

(32) Oura, K.; Hanawa, T. Surf. Sci. 1979, 82, 202-214.

(33) Chang, J. F.; Young, T. F.; Yang, Y. L.; Ueng, H. Y.; Chang, T. C. *Mater. Chem. Phys.* **2004**, 83, 199–203.

(34) Jang, J.-W.; Hayes, S.; Lin, J.-K.; Frear, D. R. J. Appl. Phys. 2004, 95, 6077-6081.

(35) Tiensuu, A.-L.; Bexell, M.; Schweitz, J.-A.; Smith, L.; Johansson, S. Sens. Actuators, A **1994**, 45, 227–236.

(36) Jing, E.; Xiong, B.; Wang, Y. J. Micromech. Microeng. 2010, 20, 095014–095014-6.

(37) Gradin, H.; Braun, S.; Stemme, G.; van der Wijingaart, W. J. Micromech. Microeng. 2009, 19, 105014–105014-9.

(38) Lin, Y.-C.; Baum, M.; Haubold, M.; Frömel, J.; Wiemer, M.; Gessner, T.; Esashi, M. Development and evaluation of AuSi eutectic wafer bonding. IEEE International Conference on Transducers, Denver, CO, June 2009.

(39) Daudin, R.; Revenant, C.; Davi, G.; Renaud, G. Phys. E 2012, 44, 1905–1909.